先进封装中铜-铜低温键合技术探讨研究进展

低温键合技术进行了综述,首先从工艺流程、 连接机理、性能表征等方面较系统地总结了热压工艺、混合键合工艺实现低温键合的研究进展与存在问题, 进一步地阐述了新型纳米材料烧结工艺在实现低温连接、降低工艺技术要求方面的优越性,概述了纳米线、纳米多孔骨 架、纳米颗粒初步实现可图形化的根据结果得出,基于纳米材料烧结连接的基础原理,继续 开发出宽工艺冗余、窄节距图形化、优良互连性能的

摩尔定律指出,集成电路上可容纳的晶体管数 目及性能约每隔18 ~ 24个月便会提升一倍.随 着大数据、5G、人工智能、移动互联网的迅猛发展, 尤其是工艺节点到7 nm之后,物理效应、成本的限 制使得依靠光刻技术驱动的摩尔定律明显放缓.在“后摩尔时代”,不再一味地追求更小的光刻工艺 节点,而是依靠先进封装互连技术的创新来满足系 统微型化、多功能化的需求,这将是集成电路制造 行业发展的重要方向之一.

为了满足高性能芯片的应用需求,未来先进封 装互连技术将不断向高密度、高可靠的方向发展.高密度即指焊点节距将不断减小至10 μm以下,焊 点密度超过10 000个/mm2;高可靠主要指焊点在 电流密度不小于106 A/cm2、服役温度不低于100 ℃等工况下服役时拥有非常良好的稳定性能,并伴随应用 领域对电子器件要求越高则上述服役参数将不断 提升.目前,主流应用的先进封装互连技术为Sn基 钎料软钎焊工艺,最重要的包含回流焊和波峰焊工艺, 其具有连接温度低(250 ~ 300 ℃)、成本低等优势.对于回流焊工艺,回流过程中可发生自对中效应和 塌陷效应,降低了对设备对中精度和基板平整度 的要求.然而,软钎焊工艺也存在诸多局限性,比如 回流过程中易发生外溢效应,没办法实现窄节距互 连;其接头载流能力弱,易发生电迁移失效;界面 反应易生成空洞和脆性相,引起机械可靠性降低等.这些瓶颈导致软钎焊工艺不足以满足未来先进 封装互连技术的发展要求.近年来,Cu-Cu键合 新方法发展迅速,无Sn元素的使用避免了上述问 题的出现.具体而言,Cu-Cu键合具有以下优势:①Cu在键合过程中全程保持固态,无软钎焊的外 溢问题,可实现窄节距互连;② 具备优秀能力的导电、 导热性能,良好的抗电迁移能力和热机械可靠性;③Cu是半导体制造中的常用金属,工艺兼容性好 且材料成本低廉.综合上述因素,Cu-Cu键合技术 可满足高密度、高可靠互连,未来最大有可能获得大 规模应用.然而,Cu-Cu键合也面临诸多新的挑战, 如铜的熔点(1 083 ℃)高、自扩散速率低,难以实现 低温键合.已有研究表明,Cu-Cu直接键合需要在400 ℃的高温下才能充分发生原子扩散,如此 高的温度会导致降低对中精度、损伤器件性能、增 加设备要求等问题.因此,怎么来实现Cu-Cu低温 键合已成为学术界和产业界共同关注的焦点之一.

目前,实现Cu-Cu低温键合的技术方法可分为 热压键合工艺、混合键合工艺、纳米材料烧结工艺 三大类.除了需满足上述低温需求外,新工艺还要 考虑性能(如强度、电阻)、可靠性、效率、成 本、工艺兼容性等因素.文中将对这些工艺的方 法、原理进行系统归纳、总结,分析其实际应用时存 在的工艺难点,并展望了Cu-Cu低温键合进一步研 究的方向,以期对未来技术发展提供参考.

热压键合工艺的基础原理与传统扩散焊工艺 相同,即上下芯片的Cu凸点对中后非间接接触,其实 现原子扩散键合的主要影响参数是温度、压力、时 间.由于电镀后的Cu凸点表面粗糙并存在一定的 高度差,所以键合前需要对其表明上进行平坦化处 理,如化学机械抛光(chemical mechanical polishing, CMP),使得键合时Cu表面能够充分接触.基于目 前研究文献,通过热压键合工艺实现Cu-Cu低温键 合的方法从机理上可分为两类,即提高Cu原子扩 散速率和防止/减少待键合Cu表面的氧化.

Juang,Shie,Ong,Liu等人提出了 电镀晶粒呈现高度(111)取向的Cu凸点用于CuCu热压键合的方法,如图1所示.已有研究表明, 在150 ~ 300 ℃条件下,Cu原子在(111)晶面上的 扩散速率比(100)、(110)晶面高3 ~ 6个数量级,晶 粒呈现高度(111)晶向的Cu凸点可以有效提升Cu原子扩散速率,降低键合温度.利用晶粒定向 生长的办法能够在300 ℃,90 MPa,10 s的条件下 完成快速键合,但是键合强度和导电性能较差.为 此研究人员进一步开发出了两步键合工艺:首 先,电镀后的Cu凸点进行CMP并使用柠檬酸清洗 去除表面氧化物,并在300 ℃,93 MPa,10 s的条件 下进行预键合;然后,在300 ℃,47 MPa的线 h进行退火处理,退火后的剪切强度达103 MPa,导电性能进一步改善.图1d显示了退火 后晶粒会长大至贯穿键合界面,从而可提高界面的结合强度.

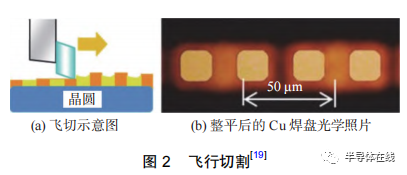

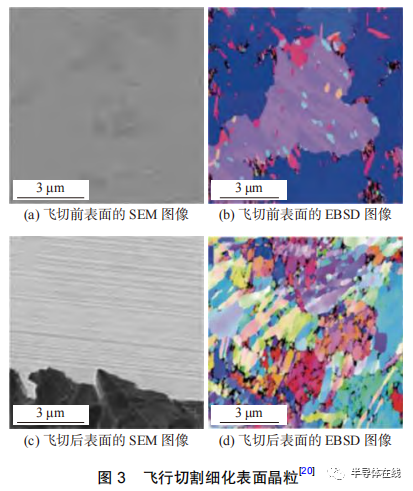

此外,Sakai等人采用金刚石刀头飞行切割 的方法对Cu表明上进行整平,如图2所示.发现切 割后的Cu表面会出现由细晶粒构成的薄层,细晶 层可提高晶界扩散通量,因而降低Cu-Cu键合的温度.最终键合在200 ℃,30 min,300 MPa的条件下 完成,且界面处原子相互扩散形成了新的晶粒.研 究人员还比较了飞行切割与CMP处理后的CuCu键合强度,根据结果得出,200 ℃连接条件下,前者 的强度比后者高出近一倍.此外,Al Farisi等人将该方法用于密封,飞行切割后的Cu密封条可在250 ℃的低温下实现键合,由此减少密封过程中的 气体解吸附,降低腔体内的气压.从图3能够正常的看到, 飞行切割后的Cu表面晶粒发生了明显细化.

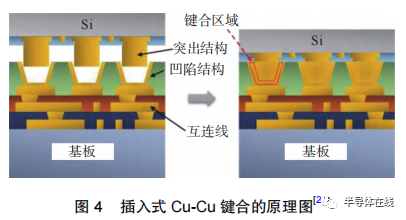

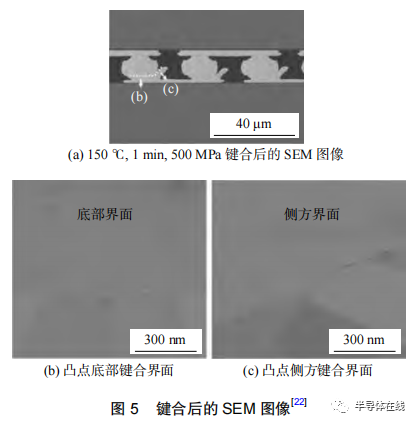

进一步地,为降低对CMP/飞行切割整平工艺 的依赖,Yang,Chou等人提出了插入式CuCu键合工艺,其原理如图4所示.首先通过电镀工 艺制作出异型结构的待键合Cu表面,一面直径较 小的Cu为突出结构,另一面直径较大的Cu为凹陷 结构,二者对中后形成插入式结构.在加压过程中突出结构的Cu和凹陷结构的Cu发生相对滑移和 应力集中,产生一定的热效应,加速原子扩散.这种 办法能够在150 ℃的条件下完成键合,键合后的界 面如图5所示.可靠性测试表明,该方法经过1 000个 热 循 环 测 试(thermal cycling test,TCT,−55 ~ 125 ℃)和96 h,130 ℃,85%湿度的加速老化测试(highly accelerated stress Test,HAST)后,接头电阻 无明显变化.这种方法无需CMP工艺,对待键合表 面的粗糙度有一定容忍度.但是 ,为了使上下Cu结构发生较大塑性变形而充分接触,需要施加 高达500 MPa以上的压力.

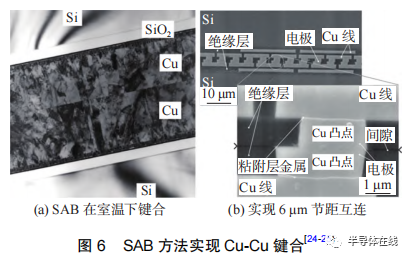

Cu在高温键合的情况下易发生氧化,阻碍Cu原子的扩散. Takagi,Suga,Shigetou等人 提出了表面活化键合(Surface Activated Bonding,SAB)的方法.该方法在超高线 torr)采用等离子体轰击待键合Cu表面,去除氧化物和 其他污染物,达到原子级的表面清洁度,并在室温、 无压力条件下进行预键合.室温条件键合能够保证 有更好的对中精度,报道中SAB可实现6 μm的窄 节距互连.由图6能够正常的看到,预键合后仍存在很明显 界面,所以该方法往往需要250 ~ 300 ℃的高温退 火. SAB表面处理和键合过程都需要在高真空条件 下完成,对设备要求非常高.

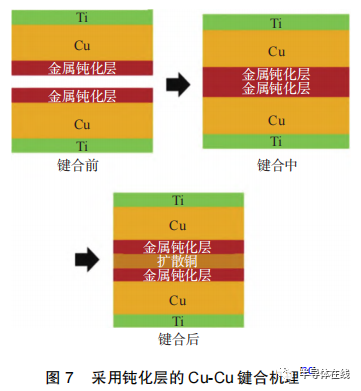

此外,研究人员提出了使用Ti,Au,Ag,Pd等金属在Cu表面制作钝化层的方法,其键合原理如图7所示. Cu表面的金属钝化层及可有效 防止Cu被氧化,在键合过程中金属钝化层会向Si基底一侧移动,而Cu原子会向键合界面迁移,最 终完成Cu-Cu键合.

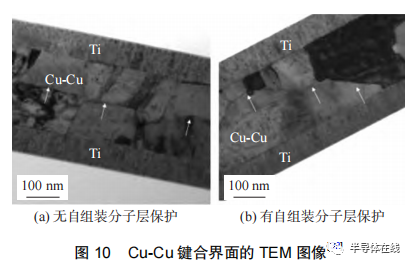

此外,Peng,Tan等人还提出了采用自组 装 分 子 层(self-assembled monolayer,SAM)钝 化Cu表面防止氧化的方法,如图9所示.在键合前, 晶圆放入烷烃硫醇溶液中进行浸泡从而在Cu表面 形成钝化保护.键合过程首先升温至250 ℃,该温 度下有机物钝化层会自行分解,随后将分解产物抽 走后,Cu-Cu键合过程在300 ℃,1 h,2 500 mbar真 空条件下进行.图10为无钝化保护和有自组装分 子层保护的键合界面对比,能够正常的看到无钝化保护的键合界面依然明显,而钝化保护的条件下界面基本消失.

窄节距互连尤其节距小于10 μm的情况下,Cu-Cu键合后的片间间隙很小,难以填充下填料.混合键合工艺可分别实现Cu和Cu之间的键合以 及Cu周围介质和介质之间的键合,键合后的介质 可起到下填料的作用,减缓热应力的同时保证更高 的键合强度、散热能力和防止Cu凸点被腐蚀.典 型的混合键合包括Cu/SiO2和Cu/粘结剂键合两 种. Cu/SiO2混合键合的关键是得到平整度高、粗糙度小、亲水性的表面,键合前需对SiO2表明上进行 激活;Cu/粘结剂混合键合基于热压键合机理,Cu/热固性的粘结剂通过加热加压的方法键合在一起.

键合后能够获得无缝隙的键合界面, 能有效提升热/机械可靠性.目前,关于CuCu键合的研究很多,如前述晶面定向生长、表面钝 化等,然而其中相当一部分工艺无法直接移植到Cu/SiO2混合键合.是因为Cu/SiO2混合键合需 要考虑Cu-Cu及SiO2-SiO2键合 ,面临工艺 兼容的挑战.目前,实现Cu/SiO2混合键合的方 法包括表面激活、直接键合技术(Direct Bonding Interconnect,DBI)、表面活化键合(SAB)等.

表面激活是指采用等离子体对晶圆表明上进行 处理,清洁晶圆表面并使其活化,研究中采用的等 离子体包括O2,H2,N2,NH3,Ar等.如图11所示,等离子体活化可以提高SiO2表面的羟 基密度,使得SiO2可在室温下实现亲水性预键合, 并在随后200 ~ 400 ℃的退火过程中脱水达成更可靠的共价键连接.基于表面激活的混合键合的难 点之一是等离子体处理会对Cu表面产生不利影 响,例如使用O2等离子体会氧化Cu,即便是Ar等 离子体处理时腔体内含有的氧也会对Cu表面造成 氧化;使用N2,NH3等处理会使得Cu表面生成 氮化物,影响Cu-Cu键合.

,Enquist等人提出了DBI的混合键合方法,其具体工艺流程如图12所示.首先通过溅 射、电镀等半导体工艺在晶圆表面制作Cu凸点,随 后沉积SiO2介质层覆盖Cu凸点及晶圆表面,接着使用标准CMP工艺露出晶圆表面的Cu焊盘并对 焊盘和SiO2介质进行整平.在CMP过程中,抛光 液作用于Cu表面使其高度略低于SiO2表面.在键 合前使用等离子体对SiO2表面进行激活,使其 可在室温、无压条件下完成预键合.预键合后需 要在300 ~ 350 ℃下进行退火,退火可以提高SiO2- SiO2之间的键合强度,并使得Cu焊盘高温膨胀相 互挤压,完成Cu-Cu键合.图13为键合后的界面,Cu-Cu及SiO2-SiO2键合界面都没有缝隙存在. DBI由于在室温下完成预键合,所以可以保证很高 的对中精度,报道称其可实现3 μm的互连节距. DBI具有良好的可靠性,键合后经过2 000个TCT (−40 ~ 150 ℃)和2 000 h,275 ℃的高温存储后,接 头电阻分别下降了1.2% ~ 1.7%和1.2% ~ 1.4%, 满足相关标准中电阻升高小于10%的要求.

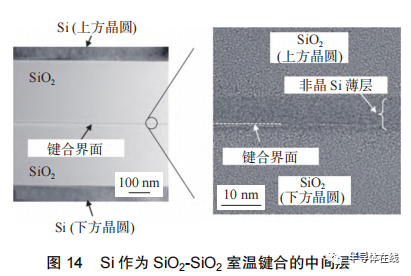

等人提出了一种基于Ar等离子体 的SAB混合键合方法.此前研究中发现,超高真空 下采用Ar等离子体轰击可以实现Cu-Cu,Si-Si之 间的键合,但对SiO2-SiO2之间的键合效果较差.为 了提高SiO2-SiO2之间的键合质量 ,研究人员在SiO2表面溅射了约12 nm的Si作为中间层,随后 经过SAB处理并在室温下键合. TEM观察发现, 键合后的界面为厚度约7 nm的非晶Si薄层(如图14所示),键合强度约为25 MPa.这种方法也会 在Cu表面引入Si层,在一定程度上降低Cu的导 电性.

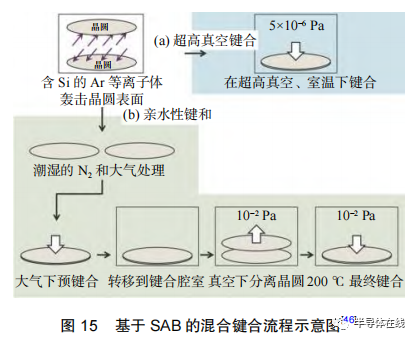

进一步地,He等人提出了采用含Si的Ar等离子体处理待键合表面的工艺方法,如图15所示.含Si等离子体可提高SiO2表面的Si点位, 促进SiO2-SiO2键合.表面处理后分两条工艺路线 进行晶圆键合,一种是直接在5 × 10−6Pa的高真空 下直接进行室温键合,另一种为采用预键合-分离-最终键合的多步路线)将处理 后的晶圆置于线Pa的腔室内,随后 向腔室内充入潮湿的N2至3 kPa,接着冲入干燥氮 气至大气压,晶圆取出后采用纯水冲洗并甩干;(2)在大气(湿度约为40%)、常温、无压条件下对晶圆进行预键合,并在大气下保存10 min以上;(3)将 预键合后的晶圆转移至键合腔室内,并在10−2 Pa的条件下分离预键合的晶圆;(4)在10−2 Pa线 min的条件下进行最终 键合并在大气压下200 ℃退火2 h.强度测试表 明,预键合—分离—最终键合的方法可实现2.0 ~ 2.5 J/m2结合能的SiO2-SiO2键合,优于高线.这是由于该方法可以在最终键合 前增加−OH吸附及去除表面H2O分子,更有利于 提高键合强度、减少界面空洞.此外,这种方法也可 以得到低含氧量的Cu-Cu键合界面.

Cu/粘结剂介质的混合键合与Cu/SiO2混合 键合类似 ,只是使用粘结剂如BCB,PBO,

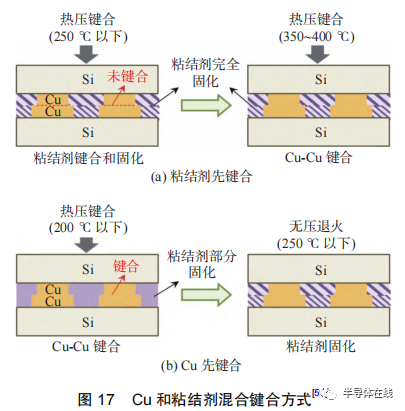

等替代了SiO2介质(图16),粘结剂具有更好 的柔性,可以一定程度上容忍介质表面的微尘颗粒物.Cu/粘结剂混合键合主要基于热压的方法,实 现方式包括两种:①粘结剂先键合,如图

在较低的温度下(约250 ℃,取决于粘结剂的种 类)首先将粘结剂键合并固化,此时Cu-Cu尚未完 成键合,然后在更高的温度(350 ~ 400 ℃)下进行 热压实现Cu-Cu键合,粘结剂在低温下键合可以防 止更高的Cu键合温度对未固化的粘结剂造成损 伤.不过这种方法存在诸多不足,如需选择耐高温 的粘结剂材料、粘结剂需要较长的固化时间导致键 合效率降低等.②Cu先键合,如图17b所示.Cu首先在低于粘结剂固化的温度下短时键合(如≤10 min),随后在更高的温度下对粘结剂进行固化 且进一步提高Cu-Cu键合的强度

实现Cu-Cu低 温键合的方法需要考虑到对粘结剂表面的影响,如Ar原子束和Ar等离子体处理虽然可以降低CuCu键合的温度,但激发出来的金属离子却会污染 粘结剂表面,干扰粘结剂的键合.为此,有研究人 员采用Pt催化后含H的甲酸对Cu和粘结剂表 面做处理,可以在200 ℃,5 min条件下完成Cu-Cu键合,并且不会对粘结剂键合产生不利影响.3 热压键合和混合键合的工艺难点

.目前大部分研究还仅仅停留在实验 室阶段,需要进一步深入对工艺和机理的探讨.

无论是热压键合还是混合键合方法对待键合表 面的质量如粗糙度、光洁度、晶圆整体翘曲程度有 很高要求.由于制作完成的Cu表面为粗糙状态且 有一定的高度差,需要经过昂贵、复杂的CMP、飞行 切割等整平工艺对待键合表明上进行平坦化,降低表 面粗糙度和高度差.此外,晶圆本身还具有一定的 翘曲,尤其是面积大、厚度薄的晶圆,翘曲程度会更 加明显

,Cu-Cu键合的“硬碰硬”接触方式易在键 合良率方面出现问题.在低温互连方面,为了实现300 ℃以下的低温互连,增大界面接触面积,往往需 要增加键合压力至100 MPa以上,这样大的压力可 能会导致晶圆碎裂或介质层开裂、变形等问题,不能 满足工艺要求.此外,混合键合中Cu-Cu键合和介 质-介质键合二者常常会相互干扰,需要兼顾两方面 的键合要求,对材料、工艺都提出了很大挑战.3.2难以灵活适用于2.5D互连

Cu/介质混合键合技术近年来发展迅速,部分 混合键合技术已在实际制造中应用于3D互连的晶 圆键合(Wafer to Wafer,W2W).然而,混合键合 技术对待键合表面的微尘颗粒物很敏感.即便如

粘结剂混合键合可以容忍一定的微尘颗粒物, 但如果颗粒物出现在Cu表面,仍会严重影响键合 质量.在2.5D互连的芯片-晶圆键合(Chip to Wafer,C2W)场合中,晶圆需要切割成单个芯片再键合到 载板晶圆表面,切割过程中不可避免地会引入微颗 粒物等,混合键合技术难以适用.此外,2.5D互连 主要是为了实现芯片功能整合,需要贴装的芯片种 类非常多样化,往往来自不同晶圆制造厂商,下游 的封装厂很难说服上游晶圆厂改变制程来适应混 合键合的工艺需求.4 Cu纳米材料烧结连接近年来,基于Cu纳米材料烧结连接实现CuCu键合逐渐获得关注.

纳米材料相对于宏观块体材料,表面原子占比增多,具有更高的表面能,更易发生原子扩散,非 常有利于在低温下进行烧结连接.以金属纳米颗粒为例,其烧结过程可以用经典 粉末烧结理论进行描述

根据粉末烧结理论,由粉 末材料构成的颗粒系统在烧结时倾向于降低其表 面的自由能,这是推进烧结进程的主要动力,烧结颈的长大是烧结过程进行的具体表现.在烧结过程 中,首先分散/疏松的纳米颗粒在压力作用下相互接 触,然后随着温度的升高发生表面扩散、晶界扩散、 晶内扩散,烧结颈逐渐长大,组织趋于致密化.烧结后的组织为多孔结构,与块体材料相比具有更小的模量,更容易发生塑性变形,对粗糙、不平整表面有 优异的

“填补”效应,具有更宽的工艺窗口.根据纳米材料烧结前的形态进行划分,研究中 的Cu纳米材料主要包括三类:纳米线、纳米多孔骨 架和纳米颗粒.下面分别对这三方面的研究现状进行简要介绍.

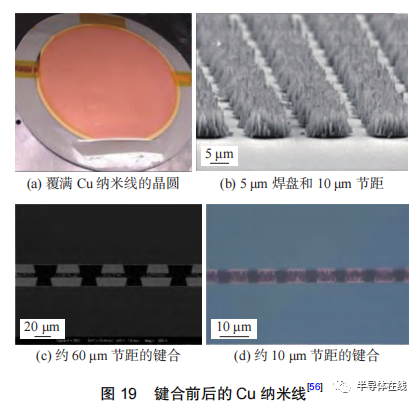

Roustaie,Strahringer,Yu等人提出了 一种基于Cu纳米线烧结的工艺,该工艺的优势主 要体现在其Cu纳米线阵列的图形化方式与成熟半 导体工艺良好兼容,可实现高密度

纳米线凸点 的制备.具体工艺流程如图18所示:①在对晶圆进 行厚胶光刻漏出Cu焊盘,Cu焊盘作为纳米线生长 的基底,光刻胶作为纳米线定向生长的掩膜;②通 过氧等离子体轰击去除Cu焊盘表面的有机物残 留;③将带有直孔阵列的特制掩模板压覆在晶圆表 面,并与Cu焊盘接触,整体浸没到Cu电镀液中;④随后进行电镀工艺,电镀过程中Cu纳米线以Cu焊盘为基底,沿着掩模版孔阵列的方向向上生 长;(5)最后去除掩模版,获得由Cu纳米线构成的 凸点阵列.这种方法可以实现凸点阵列的晶圆级制备,如图19a

所示.所获得的Cu纳米线 MPa的温度、压力条件下实现57.4 MPa的剪切强度,且经过1 000个热循环测试(−40 ~ 150 ℃)和4 000 h的HAST测试(85 ℃,85%湿 度)后剪切强度无明显下降.4.3 Cu纳米多孔骨架烧结

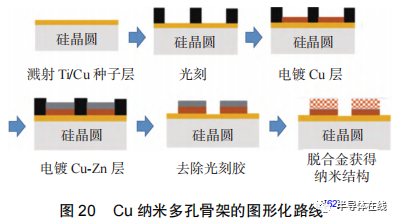

Mohan等人提出了 一种可图形化的脱合金法制备Cu纳米多孔骨架凸点,其具体工艺流程如图

所示.首先在晶圆 表面溅射一层Ti/Cu作为后续电镀工艺的种子层, 随后旋涂光刻胶并进行光刻得到所需的孔阵列图案 ,接着在光刻胶孔内分别电镀4 ~ 8 μm厚的Cu凸点和5 ~ 10 μm厚的Cu-Zn合金,光刻胶去除 后即可得到上方为Cu-Zn合金、下方为Cu的复合 凸点结构,最后使用1%质量分数的HCl在室温下 腐蚀4 h使得Cu-Zn合金中的Zn被腐蚀并获得Cu纳米多孔骨架凸点.在Cu纳米多孔骨架制备方面,研究人员主要 研究了电流密度、Cu-Zn合金中Zn的含量、退火工 艺对Cu纳米多孔骨架组织的影响,结果表明在电 流密度为

Zn含量为85%、200 ℃/ 30 min/N2退火的工艺条件下,可以获得较理想的 纳米多孔结构,如图21所示,特征尺寸在60 nm以下,其中约有10%的Zn残留.在250 ℃,9 MPa,30 min,5%甲酸气氛的键合 条件下,剪切强度可达

22所示,键合 前约3 ~ 4 μm厚的多孔纳米结构被压缩到了1 μm以内,这表明该方法可以在一定程度上通过塑性变 形弥补基板翘曲以及Cu柱高度差带来的不平整 度.不过,该工艺制备获得的Cu多孔结构中存在 一定的Zn残余,活泼金属对长期服役可靠性的影 响需要进一步研究.4.4 Cu纳米颗粒烧结

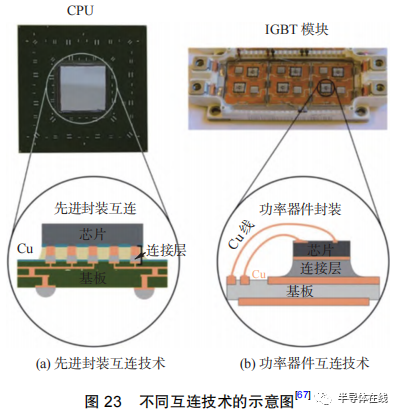

.如图23所示,功率器件封装的芯片与基板间一般只 有一个互连层,而先进封装互连的焊点数量成千上 万. Cu

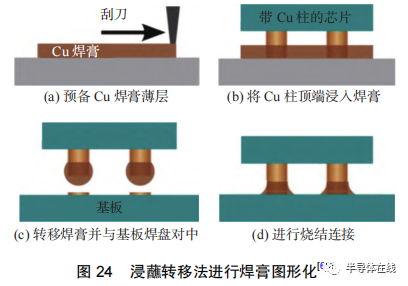

.Del Carro,Zürcher等人提出了一种浸 蘸转移的方法实现焊膏图形化 ,其具体流程如图24所示

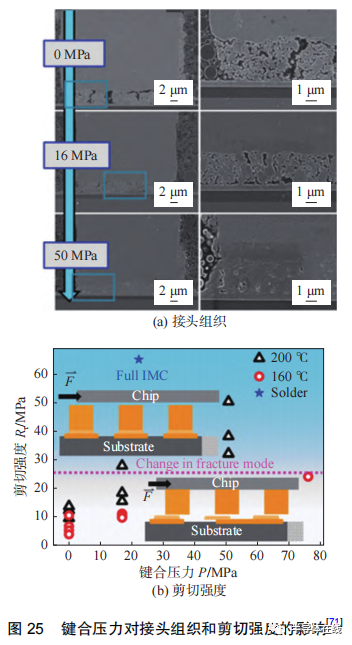

20 μm厚度的薄层 ,将电镀有Cu凸点的芯片在焊膏中浸蘸使得Cu凸点顶端黏附有8 ~ 12 μm厚度的Cu焊膏,接着将芯片与基板进行 对中并在甲酸气氛下160 ~ 200 ℃烧结键合.研究人员首先研究了Cu凸点的轮廓形态、浸 蘸转移的速度、焊膏粘度等对图形化的影响,结果 表明该方法拥有非常良好的稳定性,可以适应一定的工 艺波动.并重点分析了键合压力对界面烧结组织 和性能的影响,结果如图25

10 MPa;随着压 力增大到50 MPa,界面组织趋于致密,剪切强度提 升至40 MPa左右.该方法率先将Cu纳米焊膏应 用到先进封装互连领域,并表现出良好的适用性, 具有良好的应用前景,但相关可靠性测试数据还比较少,要进一步研究.此外,由于Cu纳米焊膏具 有一定的流动性,易在压力作用下发生挤出从而导 致相邻焊点“桥接”,所以该方法在实现窄节距互连 上面临一定局限性.此外,Mimatsu等人基于Cu纳米颗粒粉末 提出了类似的转移方法进行图形化.研究人员将通 过化学法合成的

纳米颗粒粉末铺匀到裸硅片 上,再将带金凸点的芯片与裸硅片压到一起并加热 到

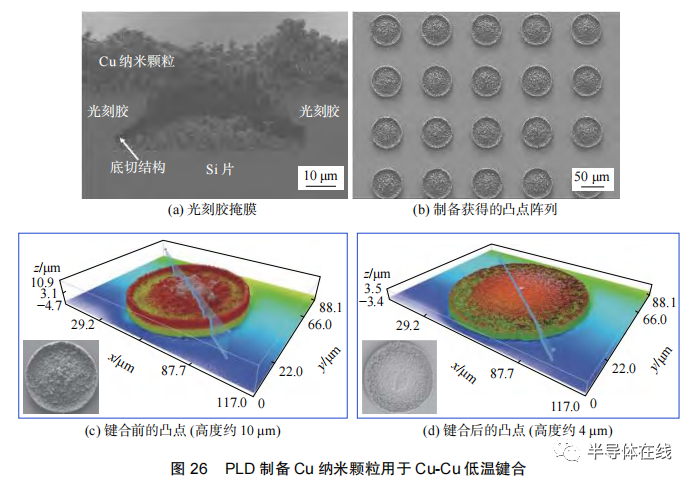

Au纳米颗粒与金凸点表面发生一 定程度的预烧结,最后将芯片与基板对中键合到一 起.这种方法最大的问题是纳米颗粒粉末与凸点间 的结合很弱,部分凸点上没有或只有很少的纳米颗 粒附着.清华大学邹贵生团队最新提出了基于脉冲激 光沉积(Pulsed Laser Deposition,PLD)技术图形化 制备Cu纳米颗粒并用于Cu-Cu低温键合的方法.如

26所示,该方法通过PLD沉积工艺制备出Cu纳米颗粒,并以光刻胶作沉积掩膜,随后剥离去 除光刻胶即可获得由纳米颗粒构成的凸点阵列(直 径60 μm、节距120 μm).在250 ℃,9 MPa,10 min, 甲酸气氛键合条件下,剪切强度达52.2 MPa,键合 前高度约10 μm的凸点被压缩至约4 μm.与具有 流动性的纳米焊膏相比,PLD制备出的纳米颗粒为全固态结构,因此加压过程中不易出现溢出导致焊 点短路的问题.此外,该方法制备出的凸点具有良 好的塑性变形能力和低温互连性能.未来可继续深 入对该方法的电学性能、服役可靠性等方面的研究.5 结论(1)随着主流Sn

键合技术凭借其 可实现窄节距、高性能互连且与半导体制造工艺兼 容性好等优势脱颖而出,成为先进封装互连的重要 发展方向

键合温度,研究人员提出 了通过晶粒定向生长、飞行切割、插入式互连结构 等方法来提高

Cu原子扩散速率以及采用等离子体 轰击、金属或有机物作钝化层来减少/防止Cu表面 氧化的方法.

(3)混合键合在窄节距互连时将Cu-Cu及介 质-介质分别键合起来,键合后的介质起到下填料的 作用,具有更优的热/机械可靠性.混合键合包括Cu/SiO2

Cu/粘结剂键合两类,键合时工艺要综合 考虑Cu-Cu键合及介质-介质键合两方面.(4)热压键合和混合键合对待键合表面的粗糙 度、光洁度、晶圆翘曲程度等有严格要求,往往需要 昂贵、复杂的平坦化工艺及较高的键合压力来保证 键合表面充分接触.此外,混合键合技术在应用于2.5D互连时也面临一定挑战.(5)近年来,基于纳米材料烧结实现Cu-Cu

.纳米材料具有低温连接、界 面填缝等优势,可降低工艺技术要求.研究人员采用定 向生长纳米线、脱合金制备纳米多孔骨架、浸蘸转 移纳米焊膏、PLD沉积纳米颗粒等方法分别实现了 焊点图形化和Cu-Cu低温键合,并在降低键合温 度、压力、适应基板翘曲等方面表现出一定潜力,但 仍需要更多的性能、可靠性测试作支撑.

Cu-Cu键合的研究还处于起 步阶段,未来继续开发出宽工艺冗余、窄节距图形 化、优良互连性能的纳米材料互连方式仍大有可为.-End-*博客内容为网友个人发布,仅代表博主个人自己的观点,如有侵权请联系工作人员删除。